Phase Change Memory - Death To Flash Memory?

Intel and ST Microelectronics have just developed the world's first demonstrable multi-level cell (MLC) device using the new phase change memory technology. Phase change memory is a new non-volatile memory technology that allows for very fast reads and writes at lower power and longer data retention than flash technology. As such, it is a potential successor to flash memory, and could ultimately replace DRAM.

What this means is Intel and ST Microelectronics have finally developed the technique to store two bits of data in each phase change memory cell, doubling its storage capacity. This allows for greater data storage density and lower costs, making phase change memory a viable alternative to flash memory.

|

How did they do this? The short explanation is Intel and ST Microelectronics used a new "programming algorithm" to create two additional states between the amorphous (0) and crystalline (1) states of the memory cell. This doubles the number of stored value from two (0 or 1) to four (00, 01, 10 or 11), allowing for two bits of data to be stored in the same cell.

Here's an explanation by Clifford Smith, the Technology Initiatives Manager of Intel's Flash Products Group on how :

On flash, we typically use a glass (floating gate/memory cell) & marbles (electrons) analogy. With single level cell flash, the glass is empty (no marbles = "0") or full of marbles (="1"). MLC differs by controlling how many marbles you put in the glass: empty = "00", 1/3 full = "10", 2/3 full = "01", and full = "11." The number of electrons you store on the floating gate alters the amount of current the flash memory cell can deliver, allowing 2 bits per cell.

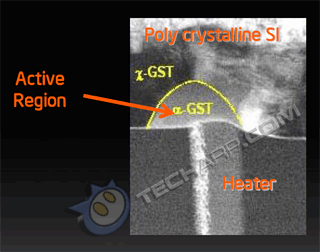

On a single level cell phase change device, a water and ice analogy works well. In an amorphous (water/liquid) state, the phase change cell does not conduct current (it's off or a "0"). When crystalline (ice), the phase change cell can conduct electricity (it's on or a "1").Switching to MLC PCM, we still rely on the liquid state as the base state (it's off or a "00"). However we need to alter our analogy slightly to accomodate 3 additional states. You can best visualize by "growing an icicle within the water." A small icicle in the water allows the cell to begin to conduct some electricity (="10"). If we grow a medium sized icicle the cell conducts more electricity (="01") and a large icicle would completely turn the cell on (="11").

In actuality the "icicle" is referred to as a crystalline filament. The point is the size of the filament (icicle) allows us to control how much current can flow through the cell, delivering 2 bits per cell.

The Techie Details

For those who love techie details, this multi-level bipolar-selected phase change memory device is built on a 90nm micro-trench technology with 9 copper interconnect layers and extensive use of low-k interlayer diaelectrics for improved power and performance. This is all integrated with lead-free packaging. The device has a capacity of 512 Mbits or 64 MB.

Previously, Intel and ST Microelectronics demonstrated 4 Mbits (0.5 MB) memory arrays on a 180nm process, and a 128 Mbit (16 MB) on 90nm using phase change memory technology. This latest device has improved on that by demonstrating a multi-level cell (MLC) device with four times the capacity.

Introduction |

||

Can you imagine - the performance of an Intel Pentium M at just 1-2 watts of power? |

||

The world's first 2 billion transistor processor, the Tukwila is also the first to feature the new QuickPath Interconnect and QuickPath integrated memory controllers. |

||

Intel and ST Microelectronics have successfully doubled the storage capacity of phase change memory. Find out how they did it! |

||

2T Gain-Cell DRAM - Future Of Larger, Cheaper Processor Cache? |

Standard SRAM are expensive in the number of transistors they require and the space they take up. Enter the new 2T gain-cell DRAM - a new on-die memory technology with double the density of SRAM! |

<<< Tukwila - 2 Billion Transistors Of Goodness : Previous Page | Next Page : 2T Gain-Cell DRAM - Future Of Larger, Cheaper Processor Cache? >>>

Add to Reddit

Add to Reddit