Silverthorne - The Future Of Mobile Internet Devices

Intel is set to launch Silverthorne in H1'08. It is a totally new processor micro-architecture designed to deliver ultra-low power (sub-1W to 2W) processors for Mobile Internet Devices. However, it is not a subset of the current Core micro-architecture, used in the Intel Core 2 desktop processors. Let's take a look at the details.

In-Order Pipeline

Unlike current CPU designs, which are all based on out-of-order execution, it goes back to an in-order design. The Silverthorne will have a dual-code, dual-issue, in-order pipeline with HyperThreading. According to Justin, HyperThreading will work better with the in-order design than it did with the out-of-order design of desktop processors.

Processor Caches

The Silverthorne processor will have 32KB instruction and 24KB data L1 caches.

The Silverthorne processor will have 32KB instruction and 24KB data L1 caches.

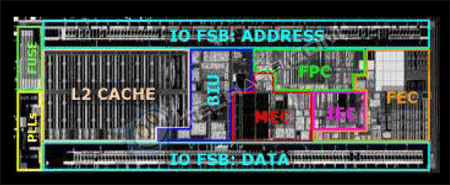

It also has a large 512KB L2 cache, which takes up about 1/3 of the processor die in this micrograph of the Silverthorne processor.

Performance

According to Justin, the Silverthorne processor will be roughly as fast as the Intel Pentium M mobile processor, used in the first-generation Intel Centrino platform. He could not tell us whether that was on a clock-to-clock basis or what the range of clock speed would be. However, Intel is hoping to eventually deliver a 2 GHz Silverthorne processor that would consume only 1 watt of power.

Compatibility

The Silverthorne may be based on the new IA micro-architecture, which is different from the Core micro-architecture used in the current Intel Core 2 desktop processors, but it is fully compatible with the Intel Core 2 Duo instruction set. That means it has the full range of capabilities as an Intel Core 2 Duo processor.

Power

The Silverthorne will consume about 10X less power than an ultra-low voltage Dothan mobile processor, thanks to its 45 nm high-k metal gate fabrication process, support for C6 deep power down and a split voltage IO (input-output) power supply.

The Silverthorne also implements a dual mode IO buffer where both legacy Gunning Transistor Logic (GTL) signaling and a full CMOS swing can be supported with a fuse-able option. In CMOS mode, the buffer can reliably transmit data at 400-533 MTs/ while reducing the total Front Side Bus (FSB) power up to 2.5x, when compared to GTL in an ISO-slew rate comparison.

System On A Chip (SoC)

Intel did not state whether Silverthorne or the new IA micro-architecture would form the basis of a future System-On-A-Chip (SoC) platform. However, this is what they had to say, "The Menlow platform is Intel's first generation platform targeted for Mobile Internet Devices. In parallel, Intel is also pursuing the Moorestown platform which comprises of a SoC and a Communication Hub for 2009/10. This SOC does integrate the processor, graphics, video and memory controller on a single chip and brings the 45nm process benefits to the complex."

Introduction |

||

Can you imagine - the performance of an Intel Pentium M at just 1-2 watts of power? |

||

The world's first 2 billion transistor processor, the Tukwila is also the first to feature the new QuickPath Interconnect and QuickPath integrated memory controllers. |

||

Intel and ST Microelectronics have successfully doubled the storage capacity of phase change memory. Find out how they did it! |

||

2T Gain-Cell DRAM - Future Of Larger, Cheaper Processor Cache? |

Standard SRAM are expensive in the number of transistors they require and the space they take up. Enter the new 2T gain-cell DRAM - a new on-die memory technology with double the density of SRAM! |

<<< Upcoming Intel Processor & Memory Technologies : Previous Page | Next Page : Tukwila - 2 Billion Transistors Of Goodness >>>

Add to Reddit

Add to Reddit