Nehalem Details

|

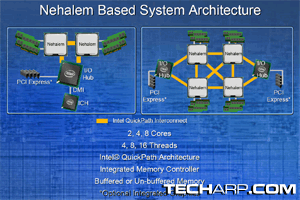

The Nehalem will be the first processor to move away from the ubiquitous Front Side Bus and add on an integrated memory controller. It is about time! AMD had already shown the way years ago, but only with Nehalem will Intel finally be able to dump the Front Side Bus and put the memory on-die.

The Front Side Bus will be replaced by Intel's QuickPath Interconnect. It will not only deliver higher bandwidth between the processor and the chipset, it will also improve bandwidth between processors in a multi-processor system. This is a critical area that AMD's HyperTransport had won much support on for years.

The on-die memory controller will also greatly improve latency and bandwidth. This is yet another area where AMD has had a great advantage in for years. Again, it was about time for Intel to play a little catch-up.

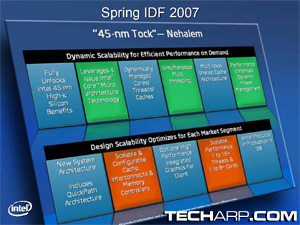

The Nehalem will also be Intel's first monolithic multi-core design. It will however feature a dynamic design, which will allow Intel to build different dies with 2, 4 or 8 cores without too much effort. In fact, Intel will also deliver some Nehalems with integrated graphics on-die.

Of course, the on-die graphics will be a mainstream solution using system memory. Pat told us that the on-die graphics will not only benefit from the closer integration but also the large shared cache. In fact, they expect to see improvements in graphics processing power between each generation improve from a paltry 20% to something like 200%.

Speaking of cache, Intel will only reveal the Nehalem's cache structure in the Spring IDF next year. But Pat says that it will be a multi-level cache with the final level shared between all cores, including on-die graphics. That sounds a lot like the AMD's triple-level cache structure.

We wondered if Intel would scavenge some broken Nehalem dies to create processors with odd-numbered cores, like the upcoming AMD Phenom tri-core processor. Pat quipped that when he heard about AMD's tri-core Phenoms, he thought it was a sign of poor yields. He said that Intel's 45 nm yields are good enough that Intel will not need to resort to such measures.

It also looks like HyperThreading is back, in the guise of Simultaneous Multi-Threading. It will allow the Nehalem to handle up to 16 threads (in the 8-core version). Good news for those who missed HyperThreading!

Parting Words

We would like to thank Pat G for taking the time to speak with us. It was a great opportunity to have met and talked shop with him. If you have not already done so, we would recommend you take a look at these related articles :

- Intel 45nm Core 2 Desktop Processor Pre-Launch Update

- Intel Developer Forum 2007 Report

- ED#57 : The AMD Phenom Goes Triple Core!

- AMD Quad-Core Opteron (Barcelona) Technology Report Part 1

- AMD Quad-Core Opteron (Barcelona) Technology Report Part 2

Topic |

Details |

|

|

Tick Tock! |

Pat talks about Intel's tick-tock candence and how it's helping them deliver processors like Nehalem, Westmere and Sandy Bridge on time. |

|

|

45nm Transition |

Pat talks about Intel's transition from 65 nm to 45 nm. |

|

|

High-K Metal Gate Transistors |

Pat talks about the new hafnium-based metal gate transistors and how this revolutionary new technology will help Intel improve their processors. |

|

|

The Penryn Family |

Pat reveals some secrets on the upcoming Penryn processors, including what's in store for Q3'08. |

|

|

Nehalem Details |

If you are wondering about Nehalem, then make sure you check out what Pat has to say about Nehalem! |

Questions & Comments

If you have a question or comment on this editorial, please feel free to post them here!

| Date | Revision | Revision History |

05-10-2007 |

1.0 |

Initial Release. |

Add to Reddit

Add to Reddit