Improved Power Management

The Barcelona boasts numerous enhancements to improve power efficiency. It involves the combination of improved power management capabilities with better manufacturing processes and additional hardware features. You may think that adding these additional features will increase transistor count and power consumption. On the contrary. The implementation of these features in hardware will actually reduce CPU overhead and therefore improve power efficiency.

The new Barcelona processors will be built on the 65 nm process using Silicon On Insulator (SOI) technology. This allows for higher clock speeds, lower voltages and reduces the processor's power consumption by reducing parasitic capacitance of the transistors. Let's take a look at the other improvements in the Barcelona's power management features.

Improved Core Power Management

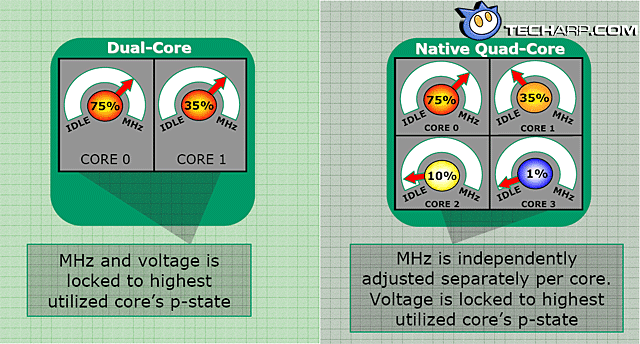

In the current dual-core Opteron processors, the clock frequency and voltage of each core is locked to the most active core's p-state. In the example below, Core 1 will be forced to run at the same clock speed and voltage as Core 0 even though it has a far lower processing load. For a better understanding of processor p-states, please take a look at our PC Power Management Guide.

AMD improves on that in the Barcelona by locking the frequency of each core to the core's actual p-state, instead of locking it to the p-state of the most active core. This allows each core to run at a lower frequency when they are under lower processing loads, reducing the processor's power consumption. However, the core voltage is still locked to the p-state of the most active core.

Advanced Clock Gating

The Barcelona has an advanced logic design with additional clock gating of the transistors. A clock gater is a hardware switch that turns off the clock to areas of logic that are not used. This allows the processor to reduce power consumption whenever any logic is not in use.

The Barcelona features two different types of clock gaters - coarse gaters and fine gaters.

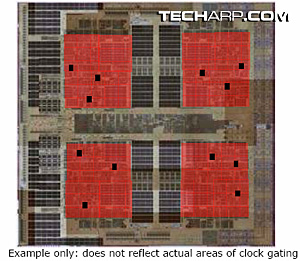

Coarse gaters shut down whole blocks of logic at a time (coloured red in the example below). When such large blocks of logic are shut down, the processor saves a lot of power. However, these coarse gaters are only useful if an entire logic area is not in use.

|

For improved power efficiency, the Barcelona can use fine gaters to shut down pieces of logic that are not active (coloured black in the example). This allows the processor to reduce power consumption even when the logic block is in use.

The combination of coarse and fine gaters allow the Barcelona to achieve much better power efficiency than the current Opteron dual-core processors without reducing performance.

<<< New Cache Structure, Monolithic Design Advantage : Previous Page | Next Page : Improved Power Management - Split Plane Power, Power Comparison >>>

Add to Reddit

Add to Reddit